AvroraZ

An introduction to Avrora emulator

Avrora is a cycle-accurate instruction-level simulator for the AVR microcontroller and for sensor networks built on the AVR microcontroller. Since Avrora is implemented in Java, the object-oriented design therefore lends itself to encapsulating the principal concepts in simulation such as instructions, devices, and state in an intuitive manner.

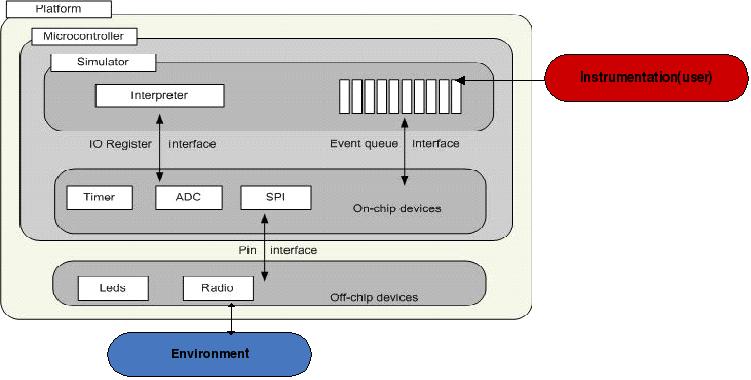

Avrora’s architecture allows a model of each device to be built in software that emulates the device and allows the program to interact with it. Each device model is written in Java and connects to the main simulation through interfaces that separate it from the details of the simulator implementation.The centerpiece of Avrora is the simulator class which consists of the interpreter and the event queue. The interpreter executes every assembly instruction of the program, while the event delta queue carries out the cycle-accurate instruction-level simulation and enables sleep optimization when the microcontroller is in idle mode. On-chip devices communicate with the simulator through the I/O register interface and the event queue interface. The microcontroller interface encapsulates an instance of the simulator class and supplies the on-chip devices such as the timer and the analog digital converter. Finally, the platform interface encapsulates the microcontroller class and supplies the off-chip devices such as the radio and LEDs. The external devices communicate with the microcontroller through the pin interface.

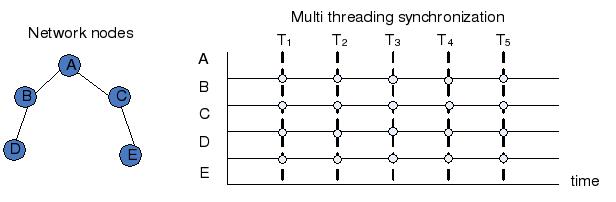

Avrora offers three core instrumentation mechanisms: probes, watches, and events. This dynamic instrumentation allows adding arbitrary profiling behavior at any point in the program or in response to any type of event at any point in simulation time, without making any modifications to the simulator or influencing the program’s behavior or timing. Avrora multi-node simulation is created by means of separate instances of the simulator class, each with its own local simulation time, and running in its own thread. The threads run in parallel and they periodically synchronize to a global clock (inserting periodic events into the queue) in order to manage the state of the environment –i.e. the radio communication channel. In terms of scalability, since Avrora runs one thread per node, the number of nodes that can be simulated is only limited by the host operating system's limit in the number of threads per process. Those threads synchronize only when necessary to ensure that the global timing and order of radio communications are preserved during simulation. Avrora authors showed in their experiments that Avrora can handle up to 1750 nodes on a dual processor server. However, it achieves greater than real hardware system performance only for networks of less than 25 nodes.

AvroraZ extensions: enabling IEEE 802.15.4 compliant emulations

AvroraZ adds support for the IEEE 802.15.4 standard compliant radio chip CC2420 from TI to the original Avrora implementation. It includes an indoor radio model to support Received Signal Strength Indicator (RSSI) and correlation values of the CC2420 radio chip, which permits LQI measurements, ED detection and CCA necessary for the implementation of the CSMA-CA algorithm in the MAC layer. Additionally, address recognition and acknowledgement of frames have also been added since their hardware support is being carried out by standard compliant radio chips. It improves the monitoring of application including printing of variables, format output for 802.15.4 sniffers and cc2420 battery monitor. AvroraZ has been tested with tinyos-1.x, tinyos-2.x and sos-2.x example applications as well as with the Open-ZB ( IEEE 802.15.4 protocol stack).